# PATENT ABSTRACTS OF JAPAN

(11)Publication number:

05-037311

(43) Date of publication of application: 12.02.1993

(51)Int.Cl.

H03K 5/00 G11B 20/18 // G11B 20/10

(21)Application number: 03-188723

(71)Applicant: ADVANTEST CORP

(22)Date of filing:

29.07.1991

(72)Inventor: HAYASHI YOSHIO

# (54) JITTER ADDING DEVICE

## (57)Abstract:

PURPOSE: To freely change the waveform and the period, and the rocking width of a jitter by preparing in advance various phase data in an external memory, and transferring the phase data to a storage device for constituting a phase data generator from the external memory.

CONSTITUTION: A storage device 22B for constituting a phase data generator 22 can by constituted of a RAM. By constituting the storage device 22B of the RAM, phase data can be rewritten. The phase data can be rewritten by a controller 25 consisting of a microcomputer, and to this controller 25, an external memory 26 is connected, and in the external memory 26, the phase data having various patterns is prepared in advance. Also, the phase data prepared in the external memory 26 can be written in the storage device 22B as necessary. In such a manner, the jitter having various waveforms, amplitude and repeat frequencies can be generated.

# (19)日本国特計庁(JP) (12) 公開特許公報(A)

FΙ

(11)特許出願公開番号

# 特開平5-37311

(43)公開日 平成5年(1993)2月12日

(51)Int.Cl.<sup>5</sup>

識別記号

庁内整理番号

技術表示箇所

H 0 3 K 5/00

T 7402-5 J

G11B 20/18

A 9074-5D

# G 1 1 B 20/10

321 E 7923-5D

審査請求 未請求 請求項の数1(全 10 頁)

(21)出顯番号

特願平3-188723

(71)出願人 390005175

株式会社アドバンテスト

東京都練馬区旭町1丁目32番1号

(22)出願日

平成3年(1991)7月29日

(72)発明者 林 美志夫

東京都練馬区旭町1丁目32番1号 株式会

社アドバンテスト内

(74)代理人 弁理士 草野 卓

### (54) 【発明の名称】 ジッタ付加装置

# (57) 【要約】

【目的】 簡単な構成で各種の波形、ゆれ幅、周期を持 つジッタをパルス列に付加することができるジッタ付加 装置を提供する。

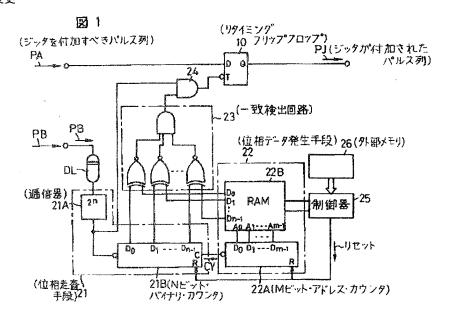

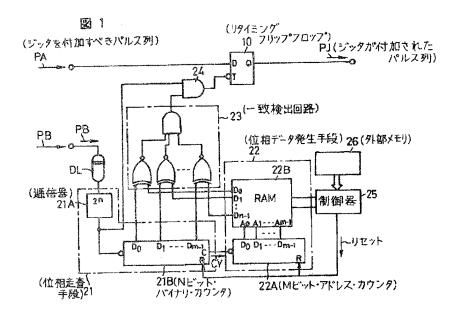

【構成】 ジッタを付加すべきパルス列PAがデータ入 カ端子に与えられるリタイミングフリップフロップ10 と、パルス列に同期したクロックPBによりパルス列の 周期内を細分化し、この細分化した位相位置を走査する 位相走査手段21と、この位相走査手段21によって走 査する各位相位置のいずれか一つにおいてリタイミング フリップフロップにトリガ信号を与えるデータを発生す る位相データ発生手段22と、この位相データ発生手段 が発生する位相データと、位相走査手段の走査との一致 を検出してリタイミングフリップフロップに与えるトリ ガ信号を生成する一致検出回路23とによって構成され る。

#### 【特許請求の範囲】

【請求項1】 A. ジッタを付加すべきパルス列がデータ入力端子に与えられ、トリガ入力端子に所望のパターンで位相が変化するトリガ信号が入力されるリタイミングフリップフロップと、

B. 上記パルス列と同期したクロックにより上記パルス 列の周期内を細分化し、この細分化した各位相位置を走 査する位相走査手段と、

C. この位相走査手段によって走査する各位相位置のいずれか一つにおいて、上記リタイミングフリップフロップにトリガ信号を与えるデータを発生する位相データ発生手段と、

D. この位相データ発生手段が発生する位相データと上記走査手段の走査との一致を検出して、上記リタイミングフリップフロップのトリガ入力端子にトリガ信号を与える一致検出回路と、

によって構成したジッタ付加装置。

#### 【発明の詳細な説明】

#### [0001]

【産業上の利用分野】この発明は、例えば各種の再生装置等で発生するジッタ、あるいは伝送路で発生するジッタを人工的に発生させ、ジッタ除去回路等の試験を行うことに利用することができるジッタ付加装置に関する。 【〇〇〇2】

【従来の技術】例えば、コンパクトディスクあるいは磁気テープ等から信号を再生する場合、あるいは伝送路を通じて信号を授受する場合等においてはジッタが発生する。これらのジッタはジッタ除去回路によって除去されて良質な信号とされて再生される。例えば、ジッタ除去 回路のジッタ除去率を測定するには予め規定されたジッタを含む信号が必要となる。このような目的のためにジッタ付加装置が用いられ、ジッタ付加装置によってパルス列に規定のジッタを付加し、このジッタが付加された

パルス列を利用して各種の試験、測定が行われる。

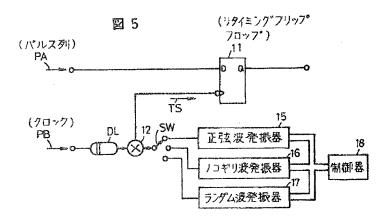

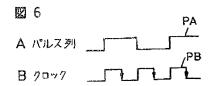

【0003】図5に従来のジッタ付加装置の構成を示す。図中11はリタイミングフリップフロップを示す。このリタイミングフリップフロップ11のデータ入力端子Dにジッタを付加すべきパルス列PA(図6A)を入力し、トリガ入力端子TにクロックPB(図6B)から生成したトリガ信号TSを入力する。トリガ信号TSは可変遅延回路12において遅延時間が変調され、この結果として出力端子Qにジッタが付加されたパルス列が出力される。

【0004】つまり、クロックPBは固定遅延素子DLによって立下りのタイミングがパルス列PAの中央に位置するように設定され、可変遅延回路12に与えられる。可変遅延回路12は例えば図7に示すように、抵抗回路12Aとバリキャップのような可変容量素子12Bによって構成することができ、可変容量素子12Bに発振器15、16、17のいずれか一つから正弦波、鋸

歯状波、ランダム波等の変調信号を与えることにより、これら変調信号の波形に従って可変遅延回路12の遅延時間が変化し、トリガ信号TSに各種パターン(波形)のジッタが与えられる。このジッタを含むトリガ信号TSによってパルス列PAがリタンミングされ、ジッタのゆらざの波形、ゆらずの繰返し周波数は、発振器15.16.17から与える変調信号によって決定される。このために切替スイッチ13が設けられ、この切替えによって夢遅延回路12に与える変調信号を選択できるように構成される。18は各発振器15、16、17の発振周波数、振幅等を設定し、制御する制御器を示す。

#### [0005]

【発明が解決しようとする課題】図5に示したジッタ付加装置によれば波形の種類だけ発振器が必要となり、効率が悪い。また各発振器15,16,17の発振周波数、振幅等を制御するには、各発振器15,16,17に使われている抵抗器、コンデンサ等の素子を切替え、定数を変更する等の構成が必要となるため回路規模が大きくなり、コストが高くなる欠点がある。

【0006】この発明の目的は簡単な構成によって付加するジッタの波形、振幅および繰返し周波数を切り替えることができるジッタ付加装置を提供しようとするものである。

#### [0007]

【課題を解決するための手段】この発明では、ジッタを付加すべきパルス列の1周期をN等分に細分化し、この細分化した各位相位置を走査する位相走査手段と、この位相走査手段で走査するいずれか一つの位相位置において、リタイミングフリップフロップにトリガ信号を与えるデータを発生する位相データ発生手段と、この位相データ発生手段が発生する位相データと走査手段の走査との一致を検出してリタイミングフリップフロップのトリガ入力端子にトリガ信号を与える一致検出回路と、によってジッタ付加装置を構成したものである。

【0008】この発明によれば、ジッタを付加すべきパルス列の1周期がN等分に細分化され、その細分化された各位相位置において、位相データ発生手段から出力される位相データと一致するごとに、その位相位置でトリガ信号を発生させる。位相データ発生手段から出力される位相データを適宜に設定することによってジッタの波形、繰返し周波数、振幅を選定することができる。

【0009】従って、この発明によれば位相データを各種用意することにより、ジッタの波形および繰返し周波数、振幅を自由に選ぶことができ、小規模の回路構成で多種の波形、振幅、繰返し周波数を持つジッタを付加することができる。

### [0010]

【実施例】図1にこの発明の一実施例を示す。図1にお

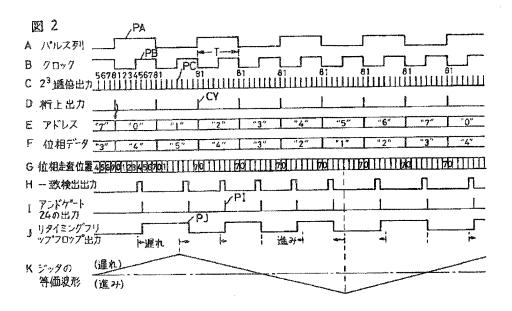

いて10はリタイミングフリップフロップ、DLは固定 遅延素子を示す。この例では、この固定遅延素子DLは 図2日に示すように、クロックPBの各立下りのタイミ ングをパルス列PAの各半周期の開始タイミングに合致 させるために設けた場合を示す。

【〇〇11】この発明では、固定遅延素子DLの後段に位相走査手段21を設ける。位相走査手段21はパルス列PAの例えば半周期内を細分化し、この細分化した複数の位相位置を走査する機能を有する。構成としては固定遅延素子DLから出力されるクロックPBを2N 選近任器21Aと、Nピットバイナリカウンタ21Bとによって構成することができる。2N 逓倍器21Aの逓倍数は、この例ではN=3に選定した場合を例示して説明する。N=3に選定することによりクロックPBの8倍の周波数のクロックPC(図2C)を得ることができる。この8倍の周波数を持つクロックPCによってクロックPBの1周期下を1/8の分解能で細分化することができる。

【0013】この桁上出力信号は位相データ発生手段22に与えられる。位相データ発生手段22はMビットアドレスカウンタ22Aと、このMビットアドレスカウンタ22Aから出力されるアドレス信号によってアクセスされる記憶器22Bとによって構成することができる。ここで、M=3に選定したとすると、アドレスカウンタ22Aは3個の出力端子D0~D2を有し、この3個の出力端子D0~D2に計数値を出力する。

【0014】図2DにNビットバイナリカウンタ21Bの桁上信号CYを示す。桁上信号CYが1個出力されるごとにアドレスカウンタ22Aから出力されるアドレス信号(図2E)は0、1、2、3、4…7、0、1、2、3…と変化する。図2Fは記憶器22Bに記憶した位相データを示す。図2Fに示す位相データ4、5、4、3、2、1、2・・・は走査手段21の細分化した各位相位置、つまりNビットバイナリカウンタ21Bの計数内容に対応する。

【○○15】記憶器22Bから読み出される位相データと、位相走査手段21から出力される各位相位置を表す値とを一致検出回路23に与え、一致検出回路23において位相走査手段21の位相走査位置が位相データ発生手段22から出力される位相データと一致したとき、その一致検出出力(図2H)をアンドゲート24を通じてリタイミングフリップフロップ10のトリガ入力端子Tに与えることにより、位相データ発生手段22から出力

される位相データによって規定される位相位置でリタイミングフリップフロップ10をトリガし、リタイミングフリップフロップ10の出カPJ(図2J)を反転させることができる。

【0016】図2に示した例では、位相データが4、5、4、3、2、1、2、3、4、5…の順に出力される例を示した。従って一致検出回路23は位相位置4の位置と、位相位置5の位置と、位相位置4の位置、位相位置3、位相位置2、位相位置1、位相位置2、位相位置3の各位置で一致検出出力(図2H)を発生する。この一致検出出力をアンドゲート24に与え、このアンドゲート24で逓倍器21Aから出力されるクロックPCの一部PIを取り出し、この信号PI(図2I)をリタイミングフリップフロップ10のトリガ入力端子Tに与えることにより、リタイミングフリップフロップ10の出力端子Qから図2Jに示す信号PJを得ることができる。

【0017】信号PJの前縁および後縁は位相位置3を中心として位相位置1、2は進み位相、位相位置4、5は遅れ位相とすることができる。図2Kに信号PJに付加されたジッタの等価な波形を示す。この例では、ジッタのゆらぎの振幅が5-1=4単位、周期8クロックPBの三角波状に位相が変化するジッタを付加した場合を示す。なお、ジッタのゆらぎの振幅は記憶器22Bに記憶した位相データの最大値から最小値を差し引くことによって求められる。尚、ジッタのゆらぎの振幅はN=3の場合、振幅1単位=外部クロックPBの周期が1 $\mu$ sであったら、振幅1単位は時間換算で125 $\mu$ sである。

【0018】位相データ発生器22を構成する記憶器22日は、例えばRAMによって構成することができる。記憶器22日をRAMによって構成することにより位相データを書換えることができる。25は記憶器22日の記憶内容を書換えるための制御器(マイクロコンピュータ)を示す。この制御器25には外部メモリ26が接続され、外部メモリ26に各種のパターンを持つ位相データを用意しておき、外部メモリ26に用意した位相データを必要に応じて記憶器22日に書き込むことにより、各種の波形、振幅、繰返し周波数を持つジッタを発生させることができる。

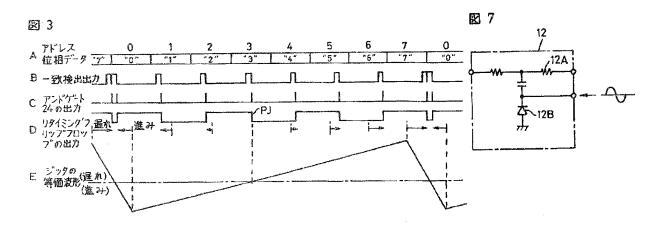

【0019】以下に、各種の位相データを記憶器22日に記憶させた場合の例を示す。図3は記憶器22日の第1アドレス0に位相データ0を記憶させ、第2アドレス1に位相データ1を記憶させ、第3アドレス2に位相データ2を記憶させ、第4アドレス3に位相データ3を記憶させ、第5アドレス4に位相データ4を記憶させ、以下同様に各アドレス5,6,7に位相データ5,6,7を記憶させた場合を示す。この場合には、一致検出回路23から出力される一致検出出力は図3日に示すように出力され、アンドゲート24からは図3Cに示すトリガ

信号が出力される。この結果、図3 Dに示すリタイミングフリップフロップの出力P」が得られる。この場合のジッタの等価波形は図3 Eに示すように振幅が7単位、周期が8 クロック P B の鋸歯状となる。

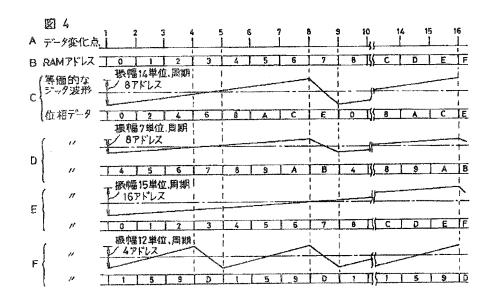

【0020】この二つの事例から明らかなように、位相データ発生手段22から出力する位相データを各種用意することによりジッタの液形、振幅、繰返し周波数の変更を容易に行うことができる。図4にN=4、M=4に採った場合の各種の位相データとジッタの等価波形を示す。N=4に採ることにより2N 逓倍器21A(図1)はクロックPBを16逓倍する。従って、この場合にはパルス列PAの半周期の1/16に細分化することになり、立相データ発生手段21は4個の出力端子を持つことになり、位相データ発生手段22を構成する記憶器22日はアドレスが16個、出力端子は4個となる。

【〇〇21】図4Aはデータの変化点、図4Bは位相データ発生手段22を構成する記憶器22Bのアドレスを示す。図4Cは記憶器22Bの各アドレスに位相データとして〇、2、4、6、8、A(10)、C(12)、E(14)を書き込んだ場合を示す。このような位相データを記憶器22Bに書き込んだ場合には、ジッタの等価的な波形は鋸歯状となる。このときジッタのゆれ幅(鋸歯状波の振幅)はE一〇=14単位、周期8アドレ

【0022】図4Dは位相データとしてアドレス $0\sim7$ に4, 5, 6, 7, 8, 9, A, B, を記憶させた場合を示す。この場合にはジッタのゆれ幅はB-4=7単位、周期8アドレスの鋸歯状となる。図4Eは位相データとしてアドレス $0\sim$ Fに0, 1, 2, 3,  $\cdots$ D, E, Fを記憶させた場合を示す。この場合には、ジッタのゆれ幅はF-0=15単位、周期16アドレスとなる。

スとなる。

【0023】図4Fはアドレス0~3に位相データとして1、5、9、Dを記憶させた場合を示す。このように 構成した場合には、ジッタのゆれ幅は12単位、周期は 4アドレスとなる。このように、この発明によれば位相 データに従ってジッタのゆれ幅および波形、繰返し周波 数を規定することができる。上述では、N=3、M=3 およびN=4、M=4の場合を例示して説明したが、実用に供する際はN=8、M=8程度に採ることが実際的である。このとき、分解能は1/128となる。この程度の分解能とすることによりジッタの波形を正弦波状、あるいはランダム波形等、各種の液形を発生させることができる。

#### [0024]

【発明の効果】以上説明したように、この発明によれば外部メモリ26に各種の位相データを用意しておき、この外部メモリ26から位相データ発生手段22を構成する記憶器22Bに位相データを転送するだけでジッタの波形と、周期およびゆれ幅を自由に変更することができる

【0025】よって、簡単な構成で多種のジッタを発生することができる。この点で安価で多種のジッタを発生することができるジッタ付加装置を提供することができ、その効果は実用に供して頗る大である。

### 【図面の簡単な説明】

- 【図1】この発明の一実施例を示すブロック図。

- 【図2】この発明の動作を説明するための波形図。

- 【図3】図2と同様の波形図。

- 【図4】図2と条件が異なる場合の動作を説明するため の波形図。

- 【図5】従来の技術を説明するためのブロック図。

- 【図6】従来の技術の動作を説明するための波形図。

- 【図7】従来の技術に用いた可変遅延回路の一例を示す 接続図。

#### 【符号の説明】

- 10 リタイミングフリップフロップ

- 21 位相走査手段

- 22 位相データ発生手段

- 23 一致検出回路

- 25 制御器

- 26 外部メモリ

[図3]

【図7】

【図1】

[図2]

[図4]

[図5]

[図6]

#### 【手続補正書】

【提出日】平成4年7月20日

【手続補正1】

【補正対象書類名】明細書

『補正対象項目名》発明の詳細な説明

【補正方法】変更

【補正内容】

【発明の詳細な説明】

[0001]

【産業上の利用分野】この発明は、例えば各種の再生装置等で発生するジッタ、あるいは伝送路で発生するジッタを人工的に発生させ、ジッタ除去回路等の試験を行うことに利用することができるジッタ付加装置に関する。 【〇〇〇2】

【従来の技術】例えば、コンパクトディスクあるいは磁気テープ等から信号を再生する場合、あるいは伝送路を通じて信号を授受する場合等においてはジッタが発生する。これらのジッタはジッタ除去回路によって除去されて良質な信号とされて再生される。例えば、ジッタ除去率を測定するには予め規定されたジッタを含む信号が必要となる。このような目的のためにジッタ付加装置が用いられ、ジッタ付加装置によってパルス列に規定のジッタを付加し、このジッタが付加された

パルス列を利用して各種の試験、測定が行われる。

【0003】図5に従来のジッタ付加装置の構成を示す。図中11はリタイミングフリップフロップを示す。このリタイミングフリップフロップ11のデータ入力端子Dにジッタを付加すべきパルス列PA(図6A)を入力し、トリガ入力端子にクロックPB(図6B)から生成したトリガ信号TSを入力する。トリガ信号TSは可変遅延回路12において遅延時間が変調され、この結果として出力端子Qにジッタが付加されたパルス列が出力される。

【0004】つまり、クロックPBは固定遅延素子DLによって立下りのタイミングがパルス列PAの中央に位置するように設定され、可変遅延回路12に与えられる。可変遅延回路12は例えば図7に示すように、抵抗回路12Aとバリキャップのような可変容量素子12Bとによって構成することができ、可変容量素子12Bに発振器15、16、17のいずれか一つから正弦波、鋸歯状波、ランダム波等の変調信号を与えることにより、これら変調信号の波形に従って可変遅延回路12の遅延時間が変化し、トリガ信号TSに各種パターン(波形)のジッタが与えられる。このジッタを含むトリガ信号TSによってパルス列PAがリタイミングされ、ジッタが

付加される。このようにジッタのゆらぎの波形、ゆらぎの幅(振幅)、ゆらぎの繰返し周波数は、発振器 1 5, 1 6, 1 7 から与える変調信号によって決定される。このために切替スイッチ SWが設けられ、この切替スイッチ SWの切替えによって可変遅延回路 1 2 に与える変調信号を選択できるように構成される。1 8 は各発振器 1 5, 1 6, 1 7 の発振周波数、振幅等を設定し、制御する制御器を示す。

#### [0005]

【発明が解決しようとする課題】図5に示したジッタ付加装置によれば波形の種類だけ発振器が必要となり、効率が悪い。また各発振器15,16,17の発振周波数、振幅等を制御するには、各発振器15,16,17に使われている抵抗器、コンデンサ等の素子を切替え、定数を変更する等の構成が必要となるため回路規模が大きくなり、コストが高くなる欠点がある。

【 O O O 6 】この発明の目的は簡単な構成によって付加するジッタの波形、振幅および繰返し周波数を切り替えることができるジッタ付加装置を提供しようとするものである。

#### [0007]

【課題を解決するための手段】この発明では、ジッタを付加すべきパルス列の1周期を等分に細分化し、この細分化した各位相位置を走査する位相走査手段と、この位相走査手段で走査するいずれか一つの位相位置において、リタイミングフリップフロップにトリガ信号を与えるデータを発生する位相データ発生手段と、この位相データ発生手段が発生する位相データと走査手段の走査との一致を検出してリタイミングフリップフロップのトリガ入力端子にトリガ信号を与える一致検出回路と、によってジッタ付加装置を構成したものである。

【0008】この発明によれば、ジッタを付加すべきパルス列の1周期がN等分に細分化され、その細分化された各位相位置において、位相データ発生手段から出力される位相データと一致するごとに、その位相位置でトリガ信号を発生させる。位相データ発生手段から出力される位相データを適宜に設定することによってジッタの波形、繰返し周波数、振幅を選定することができる。

【0009】従って、この発明によれば位相データを各種用意することにより、ジッタの波形および繰返し周波数、振幅を自由に選ぶことができ、小規模の回路構成で多種の波形、振幅、繰返し周波数を持つジッタを付加することができる。

#### [0100]

【実施例】図1にこの発明の一実施例を示す。図1において10はリタイミングフリップフロップ、DLは固定 遅延素子を示す。この例では、この固定遅延素子DLは 図2Bに示すように、クロックPBの各立下りのタイミ ングをパルス列PAの各半周期の開始タイミングに合致 させるために設けた場合を示す。 【〇〇11】この発明では、固定遅延素子DLの後段に位相走査手段21を設ける。位相走査手段21はパルス列PAの例えば半周期内を細分化し、この細分化した複数の位相位置を走査する機能を有する。構成としては固定遅延素子DLから出力されるクロックPBを2N 逓倍器21Aと、Nビットパイナリカウンタ21Bとによって構成することができる。2N 逓倍器21Aの逓倍数は、この例ではN=3に選定した場合を例示して説明する。N=3に選定することによりクロックPBの8倍の周波数のクロックPC(図2C)を得ることができる。

【0012】 逓倍器21Aで8倍の周波数に変換された クロックPCは、Nビットバイナリカウンタ21Bに入力され、このNビットバイナリカウンタ21Bによって計数される。Nビットバイナリカウンタ21BはN=3とすれば3個の出力端子 $D_0 \sim D_2$ を有し、この出力端子 $D_0 \sim D_2$ に順次計数値が出力される。これと共に桁上出力端子Cに桁上出力信号CYが出力される。

【0013】この桁上出力信号は位相データ発生手段22に与えられる。位相データ発生手段22はMビットアドレスカウンタ22Aと、このMビットアドレスカウンタ22Aから出力されるアドレス信号によってアクセスされる記憶器22Bとによって構成することができる。ここで、M=3に選定したとすると、アドレスカウンタ22Aは3個の出力端子D0~D2を有し、この3個の出力端子D0~D2に計数値を出力する。

【 O O 1 4 】 図 2 D に N ビットバイナリカウンタ 2 1 B の桁上信号 C Y を示す。桁上信号 C Y が 1 個出力される ごとにアドレスカウンタ 2 2 A から出力されるアドレス 信号(図 2 E )は O 、1、2、3、4 … 7、0、1、2、3 … と変化する。図 2 F は記憶器 2 2 B に記憶した 位相データを示す。図 2 F に示す位相データ 4、5、4、3、2、1、2・・・は走査手段 2 1 の細分化した 各位相位置、つまり N ビットバイナリカウンタ 2 1 B の 計数内容に対応する。

【0015】記憶器22Bから読み出される位相データと、位相走査手段21から出力される各位相位置を表す値とを一致検出回路23に与え、一致検出回路23において位相走査手段21の位相走査位置が位相データ発生手段22から出力される位相データと一致したとき、その一致検出出力(図2H)をアンドゲート24を通じてリタイミングフリップフロップ10のトリガ入力端子Tに与えることにより、位相データ発生手段22から出力される位相データによって規定される位相位置でリタイミングフリップフロップ10をトリガし、リタイミングフリップフロップ10の出力PJ(図2J)を反転させることができる。

【0016】図2に示した例では、位相データが4.

5、4、3、2、1、2、3、4、5…の順に出力される例を示した。従って一致検出回路23は位相位置4の位置と、位相位置4の位置と、位相位置4の位置、位相位置3、位相位置2、位相位置1、位相位置2、位相位置3の各位置で一致検出出力(図2H)を発生する。この一致検出出力をアンドゲート24で逓倍器21Aから出力されるクロックPCの一部PIを取り出し、この信号PI(図2I)をリタイミングフリップフロップ10のトリガ入力端子Tに与えることにより、リタイミングフリップフロップ10の出力端子Qから図2Jに示す信号PJを得ることができる

【0017】信号PJの前縁および後縁は位相位置3を中心として位相位置1,2は進み位相、位相位置4,5 は遅れ位相とすることができる。図2Kに信号PJに付加されたジッタの等価な波形を示す。この例では、ジッタのゆらぎの振幅が5-1=4単位、周期8クロックPBの三角波状に位相が変化するジッタを付加した場合を示す。なお、ジッタのゆらぎの振幅は記憶器22Bに記憶した位相データの最大値から最小値を差し引くことによって求められる。尚、ジッタのゆらぎの振幅はN=3の場合、振幅1単位=外部クロックPBの周期が1 $\mu$ sであったら、振幅1単位は時間換算で125nsである。

【0018】位相データ発生器22を構成する記憶器22Bは、例えばRAMによって構成することができる。記憶器22BをRAMによって構成することにより位相データを書換えることができる。25は記憶器22Bの記憶内容を審換えるための制御器(マイクロコンピュータ)を示す。この制御器25には外部メモリ26が接続され、外部メモリ26に各種のパターンを持つ位相データを用意しておき、外部メモリ26に用意した位相データを必要に応じて記憶器22Bに書き込むことにより、各種の波形、振幅、繰返し周波数を持つジッタを発生させることができる。

【0019】以下に、各種の位相データを記憶器22日に記憶させた場合の例を示す。図3は記憶器22日の第1アドレス0に位相データ0を記憶させ、第2アドレス1に位相データ1を記憶させ、第3アドレス2に位相データ3を記憶させ、第4アドレス3に位相データ3を記憶させ、第5アドレス4に位相データ4を記憶させ、第5アドレス4に位相データ4を記憶させ、第5アドレス5.6.7に位相データ5.6.7を記憶させた場合を示す。この場合には、一致検出回路に高齢によりによりに対した。この結果、図3口に示すように出力され、アンドゲート2.4からは図3口に示すように出力され、アンドゲート2.4からは図3口に示すように扱いカウンの場合が出力される。この結果、図3口に示すリタイラのジッタの等価液形は図3日に示すように振幅が7単位、周期が8クロックPBの鋸歯状となる。

【〇〇20】この二つの事例から明らかなように、位相

データ発生手段22から出力する位相データを各種用意することによりジッタの波形、振幅、繰返し周波数の変更を容易に行うことができる。図4にN=4、M=4に採った場合の各種の位相データとジッタの等価波形を示す。N=4に採ることにより2N 逓倍器21A(図1)はクロックPBを16逓倍する。従って、この場合にはパルス列PAの半周期の1/16に細分化することになる。また位相走査手段21は4個の出力端子を持つことになり、位相データ発生手段22を構成する記憶器22Bはアドレスが16個、出力端子は4個となる。

【0021】図4Aはデータの変化点、図4Bは位相データ発生手段22を構成する記憶器22Bのアドレスを示す。図4Cは記憶器22Bの各アドレスに位相データとして0、2、4、6、8、A(10)、C(12)、E(14)を書き込んだ場合を示す。このような位相データを記憶器22Bに書き込んだ場合には、ジッタの等価的な波形は鋸歯状となる。このときジッタのゆれ幅(鋸歯状波の振幅)はE-0=14単位、周期8アドレスとなる。

【0022】図4Dは位相データとしてアドレス0~7に4、5、6、7、8、9、A、B、を記憶させた場合を示す。この場合にはジッタのゆれ幅はB-4=7単位、周期8アドレスの鋸歯状となる。図4日は位相データとしてアドレス0~Fに0、1、2、3、…D、E、Fを記憶させた場合を示す。この場合には、ジッタのゆれ幅はF-0=15単位、周期16アドレスとなる。

【0023】図4Fはアドレス0~3に位相データとして1.5.9、Dを記憶させた場合を示す。このように構成した場合には、ジッタのゆれ幅は12単位、周期は4アドレスとなる。このように、この発明によれば位相データに従ってジッタのゆれ幅および波形、繰返し周波数を規定することができる。上述では、N=3、M=3およびN=4、M=4の場合を例示して説明したが、実用に供する際はN=8、M=8程度に採ることが実際的である。このとき、分解能は1/128となる。この程度の分解能とすることによりジッタの波形を正弦波状、あるいはランダム波形等、各種の波形を発生させることができる。

#### [0024]

【発明の効果】以上説明したように、この発明によれば外部メモリ26に各種の位相データを用意しておき、この外部メモリ26から位相データ発生手段22を構成する記憶器22Bに位相データを転送するだけでジッタの波形と、周期およびゆれ幅を自由に変更することができる。

【0025】よって、簡単な構成で多種のジッタを発生することができる。この点で安価で多種のジッタを発生することができるジッタ付加装置を提供することができ、その効果は実用に供して頗る大である。

#### 【手続補正2】

【補正対象書類名】図面 【補正対象項目名】図1 【補正方法】変更

【補正内容】 【図1】